晶片設計介紹

22 April 2024

晶片簡介

晶片就是由多個電路所組成的硬體,然而中間設計涉及非常多複雜的因素,例如今天晶片裡面的電晶體已達到數億個,而且塞在一個相當小的範圍內,最重要的是真的從設計圖到製作出晶片的成本非常高昂,除了要很精密的去光刻電路外,還有各種複雜的連接電路,以及最後的封裝。

因此在晶片整個製作過程中,不單單只是台積電製程,前期的設計以及各種驗證步驟也很多,避免砸大錢卻設計出一個不能用的晶片,以及最後設計完晶片也有高深的封裝技術,讓不同的晶片能夠彼此互動。

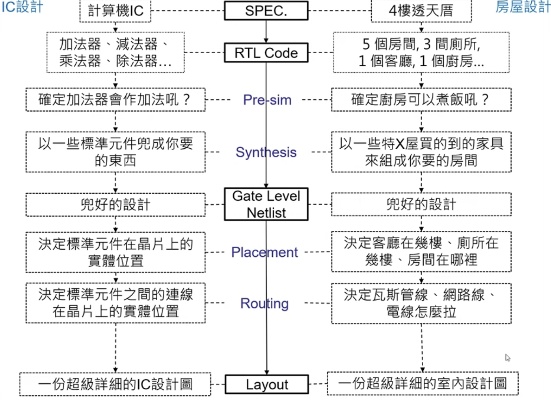

晶片製作流程概述

SPEC

首先當然是要先開SPEC, 確認這樣晶片應該有什麼功能,例如通訊晶片就應該有通訊功能,運算晶片就能運算,能支援哪些運算,儲存晶片應該要能存多少bit的資料等等

RTL code

有了SPEC後就要開始兜電路使電路能夠完成SPEC期望的輸入輸出。但是現在晶片都是上億個電晶體,因此直接繪製電路相當不實際而且也容易錯,因此工程師開發了硬體描述語言(HDL)如verilog / VHDL等等高階語言來幫助工程師設計電路。

HDL語言的好處不僅僅是更容易編寫獨董,還能夠有對應的Compiler把他編譯成RTL, 甚至最後的layout輸出,而且還能夠有更多方便的功能幫忙做前期的驗證,驗證寫出來的HDL程式碼是不是符合SPEC, 能夠產出預期的輸入輸出,也能夠驗證時間、功率等等的其他因子。

而這時期,針對verilog的程式碼驗證主要會由Synopsys的VCS來做各項變數值的模擬,並且配合Verdi來協助debug Verilog程式碼。

RTL的意思是寫出來的verilog程式碼是可以合成(Synthesis),產生layout給台積電製作,但並不是所有verilog程式碼都可以合成,verilog本身有些語法的功用只是幫忙模擬、驗證電路結果,他並不能夠合成,通常這些語法作用是在幫忙前期測試寫的RTL code的結果、輸出是否如預期。 因此Verilog寫出來的code不一定都是RTL, 但要能夠做成晶片的code一定都是RTL code。

Synthesis

合成部分就是透過compiler把寫好的HDL程式碼,變成gate level netlist, 此時就已經是電路圖,可以看到各種and/or/not gate,並且有線路連接起來。

這邊涉及很多優化,如何用更少的gate來達到相同的功能。

Placement & Routing

有了gate-level netlist後,接著就要思考該怎麼把這東西擺到晶片上面,各個元件/gate要怎麼擺,現要怎麼接才順。

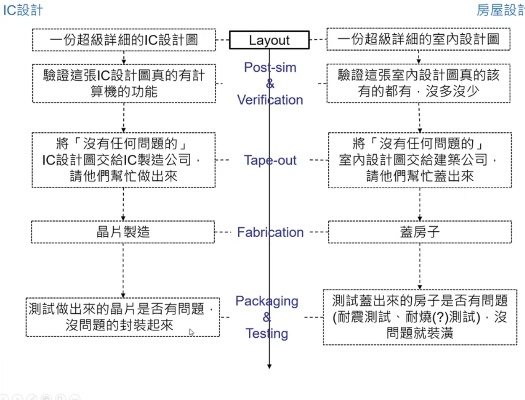

做完這部分後就真的產生一個設計藍圖(layout),接著就把這layout給台積電製作

Verification & Post-Sim

Tape-out & Fabrication

這邊基本上就是晶片製造商(tsmc, intel, samsung),根據layout設計圖製作晶片,這時候晶片就是一整大片wafer, 每一個是裸晶,可以是運算晶片、記憶晶片、通訊晶片等等。接著還要透過後續步驟把各個晶片接起來,才能形成完整的功能。

封裝&測試

封裝在先進製程中佔據相當重要的地位,是現今晶片能夠維持摩爾定律的重要技術,也是近期台積電發展的重點之一。

封裝在於把設計好的裸晶安裝在基板上,並讓各條金屬線與裸晶接好,這樣就可以透過基板上的線路向外連接,連接其他的元件、晶片,這樣運算晶片才能跟儲存晶片、通訊晶片互通。除此之外還包括給晶片上樹脂避免灰塵。

測試在於最後封裝好的晶片,透過基板上的金屬線來做測試,測試晶片運作符合SPEC。

例如CoWos就是一種封裝技術把多個晶片堆疊再一起的技術

專有名詞介紹

EDA

Electronic Design Automation,如上述所說,設計晶片有相當多且複雜的流程,需要寫相當龐大的電路、程式以及許多精密的測試。

電路、程式以及很多測試是沒辦法單靠人力來進行的,因此需要很多工具輔助,例如寫出來的verilog是否有辦法驗證邏輯正確、符合spec,設計出來電路是否能夠順利接通,時間不會有太大延遲,不會有電力相關問題,而且電路一定能塞得進晶片裡等等。

摩爾定律

Intel共同創辦人摩爾發現晶片裡的電晶體數目,每隔數年就會成倍數增長,說明整個晶片產業發展迅速,每隔幾年就有突破性發展,晶片裡電晶體數目變更多,速度變更快。

3DIC

摩爾定律有著物理極限,隨著台積電做的7nm, 5nm到後來的2nm, 其實晶片裡能塞的電晶體數目已經趨近極限沒辦法再更多。

因為電晶體運作本身會有熱能產生,當單位面積電晶體太多,會產出太多熱能,而這熱能會影響電晶體的運作。

為了讓摩爾定律能夠繼續成立,因此電晶體塞的方式從平面變成立體堆疊,這樣相同單位面積能塞的電晶體數目就增多,而這種立體堆疊的電晶體就是3DIC。

SOC

SOC: system on chip

硬體目前的一個bottle neck在於 個晶片間傳資料的速度過慢,即便傳輸不斷的在更新,usb3.0, PCIe等等的傳輸 但還是要透過bus的方式把資料從一個晶片傳到另一個晶片。

SOC的目的在於透過封裝技術來解決這個資料傳輸的bottle neck,主要概念在於把不同的晶片透過封裝裝在同一個基板上,這樣就變成一個晶片裡面其實封裝了許多不同功能的晶片,這也是Apple目前採用的技術。

這項技術難度在於要把不同的晶片封裝再一起,那他們勢必要把金屬線接好,而這件事情相當不容易,如果每家公司的晶片規格不同的話。再者將不同的晶片封裝再一起,這個晶片就會變得比單一晶片還大。

SIP / Chiplet

SIP: system in package

與SOC同樣處理晶片間資料傳輸的問題,但SIP

SIP: 將數個初步封裝的晶片在經過一個大片的封裝,與SOC相比,SOC是將所有晶片都一次封裝在一個基板上

Chiplet: 在一個晶片系統中封裝進多個不同的晶片,這些晶片可以是不同公司製造、設計的,使用不同材料等等,但這部分要連接起來就相當不容易